How Message Signaled Interrupts (MSI) Work

In this tip, you’ll learn how MSI (Message Signaled Interrupts) work using an example with PCIe.

Message Signaled Interrupt (MSI) is a method of signaling an interrupt in the form of an MSI transaction, identical to a standard memory write (WR) request.

These requests represent interrupt messages that determine which interrupt should be delivered to which processor. Unlike traditional interrupt signaling—done through dedicated lines—MSI sends messages through the main data path. While more complex to implement, MSI offers significant advantages such as improved interrupt service routine (ISR) handling and reduced interrupt latency.

MSI in PCIe

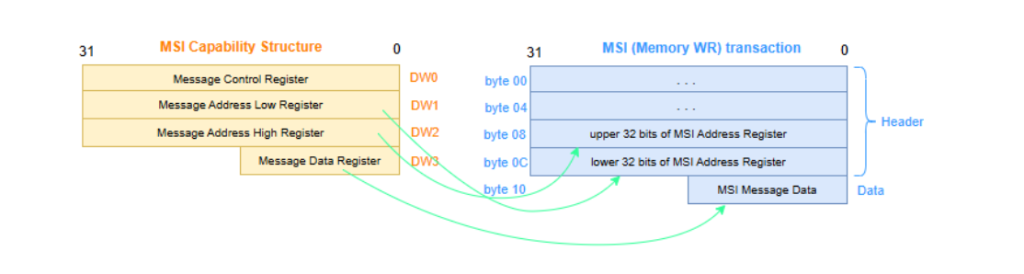

MSI is supported in PCIe. The MSI capability structure, configured by software (typically the PCI bus driver), provides all the necessary information for the device to signal an MSI.

A client can request interrupt service by initiating an MSI through configuration writes to the following registers within the MSI capability structure:

- MSI Message Address Low Register

- MSI Message Address High Register

- MSI Message Data Register

- MSI Mask Register

Finally, the MSI Control Register must be enabled to allow MSI generation.

The content of the Message Data Register is written to the memory address specified in the Message Address Register.

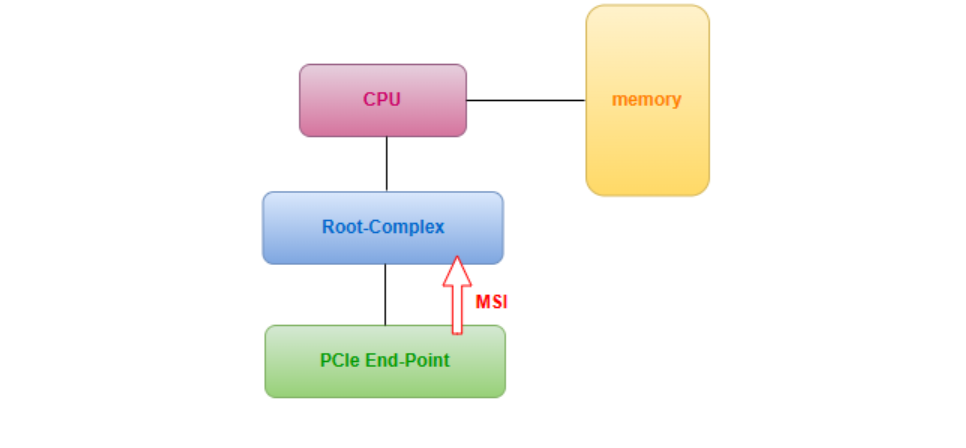

Interrupt conditions are communicated from the PCIe core—configured as an End-point—to the Root-complex via interrupt messages.

When an interrupt condition occurs on the slave interface (IF), the End-point sends a message identifying the interrupt’s origin. Each message is a memory WR request, containing an address and data value.

The client logic must, considering the configuration of the MSI registers, assign the correct address to a region register. This translates the WR transaction into a PCIe memory write TLP, which is then forwarded onto the link.

On the Root-complex side, the PCIe core decodes MSI messages received from the link and passes them to the client logic via the master IF as standard WR requests.

When the core is configured as a Root-complex, it receives MSI messages from downstream End-points and processes them just like any other memory WR request from the link.

The core transfers the address and data associated with these memory WR requests over the same target memory WR interface used for normal memory writes. Software running in the Root-complex is responsible for monitoring these writes to the MSI-assigned memory region and servicing the corresponding interrupts.