How to access out of scope signals when using SVA modules

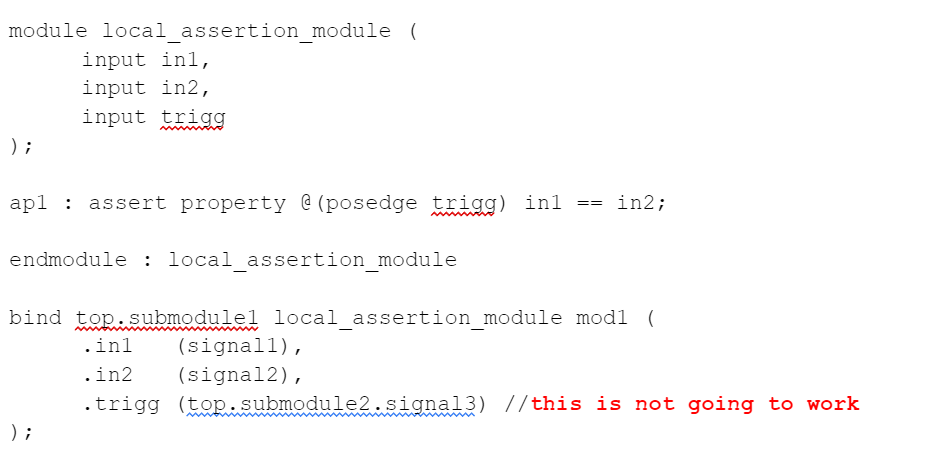

Problem: Assertions are written inside SVA modules which are instantiated, using a bind statement, on top of most hierarchy levels that have all the signals needed for assertions. Sometimes, there is not one hierarchy that contains all of the necessary signals for a single assertion.

Solution:

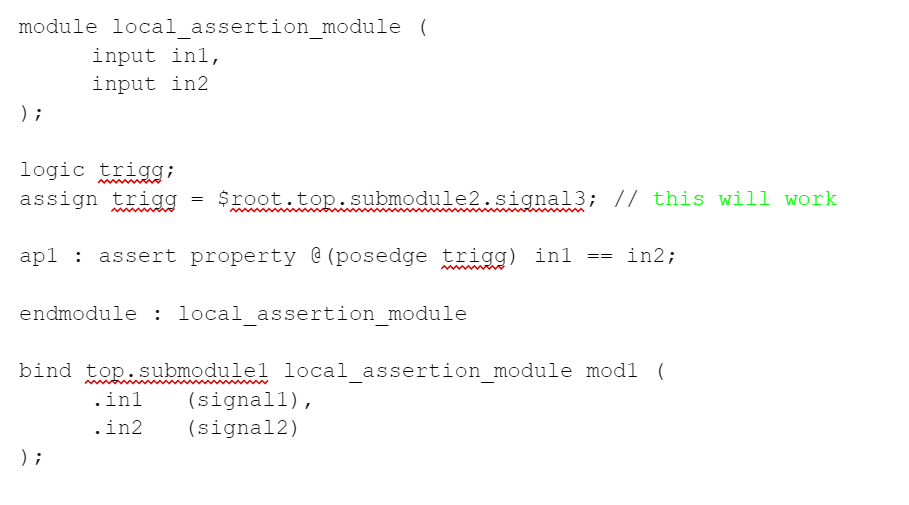

SystemVerilog system variable $root allows explicit access to the top of the instantiation tree. A signal that is out of scope for SVA module can be accessed by using $root followed by the explicit signal path.

Usage: