How to Avoid Glitches When Comparing Signals

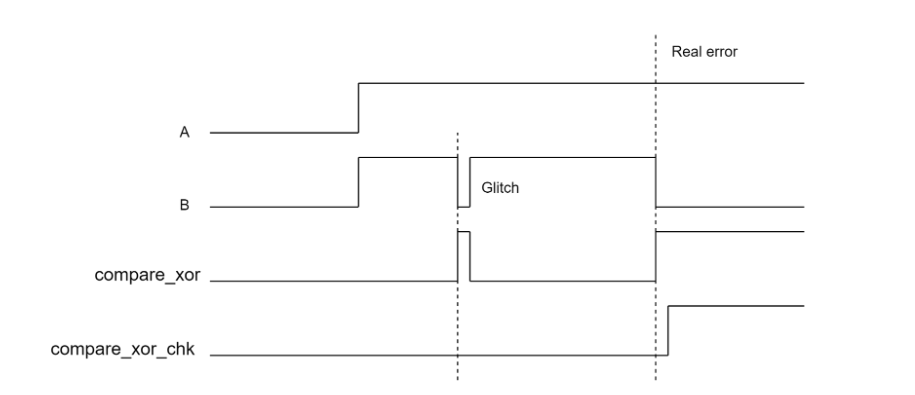

https://verilogams.com/refman/modules/assigns.html#:~:text=You%20can%20add%20delay%20to,continuous%20assign%20statements%20swallow%20glitches1. Compare equal signals that have glitchesIf, for example, you have signals A and B that are supposed to be equal. You also have glitches in signal B. How do you avoid glitches in B? By using the continuous assignment, you can avoid glitches in a signal.

If you need to compare two signals it’s easy to do so using XOR (Tips & Tricks 15. Check if signals are equal using XOR). This define will compare signals A and B, detect the glitches in B, and the checker will ignore them.

What this define is doing is comparing signal A with signal B, while using continuous assign statements to delay the change in compare_xor_chk, and avoiding the glitch. We need the id if we want to have multiple instances of this define.

2. Compare equal signals that have a small delay

Example: If B is equal to A and is delayed by 0.1ns, then we work on the assign with delay >0.1 then the compare_xor_chk will stay low and the check will pass.