Printing UVM info inside properties/assertions

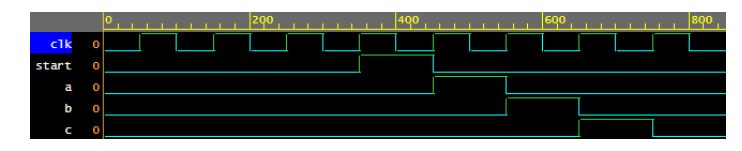

It’s possible to call UVM info from inside a property. This could be useful for logging the current status of an assertion for a property which consists of multiple steps. Here’s an example with an assertion that checks whether a, b, and c are all asserted one after another, after a start signal is asserted.

In case we need to see in the log all instances where the assertion is starting or when a, b or c are asserted, we can modify the previous property in the following way:

Just add a suitable uvm_report_info call to each step and conjoin them within a pair of brackets. The result of this when an assertion is passing is:

Note that a uvm_report_info function is used here instead of a `uvm_info macro. These two have identical purposes, but the macro can’t be used here because it inserts expressions with additional semicolons, which aren’t syntactically allowed to be placed in the middle of a property expression. Debugging assertion failures of such properties is easier if the assertion debug tools in your preferred simulator are too complicated, verbose, or unavailable.